# OS iProject Three

Alan G. Labouseur, Ph.D. Alan.Labouseur@Marist.edu

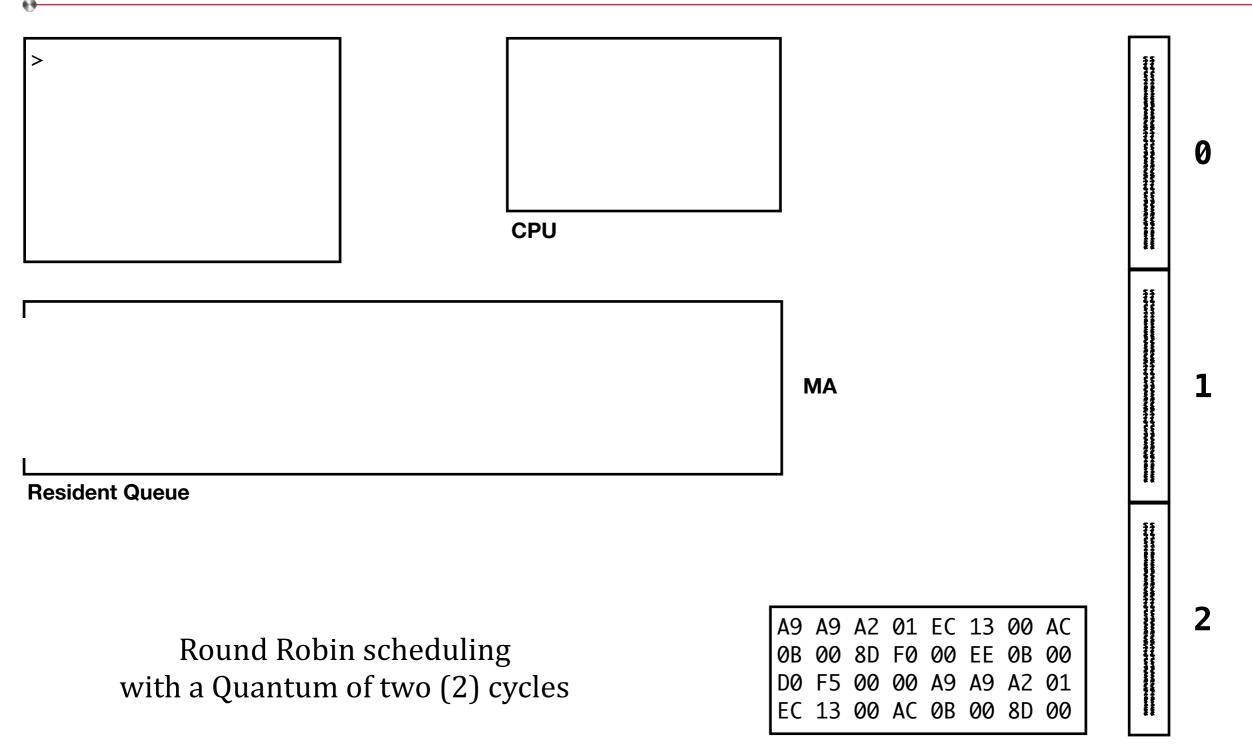

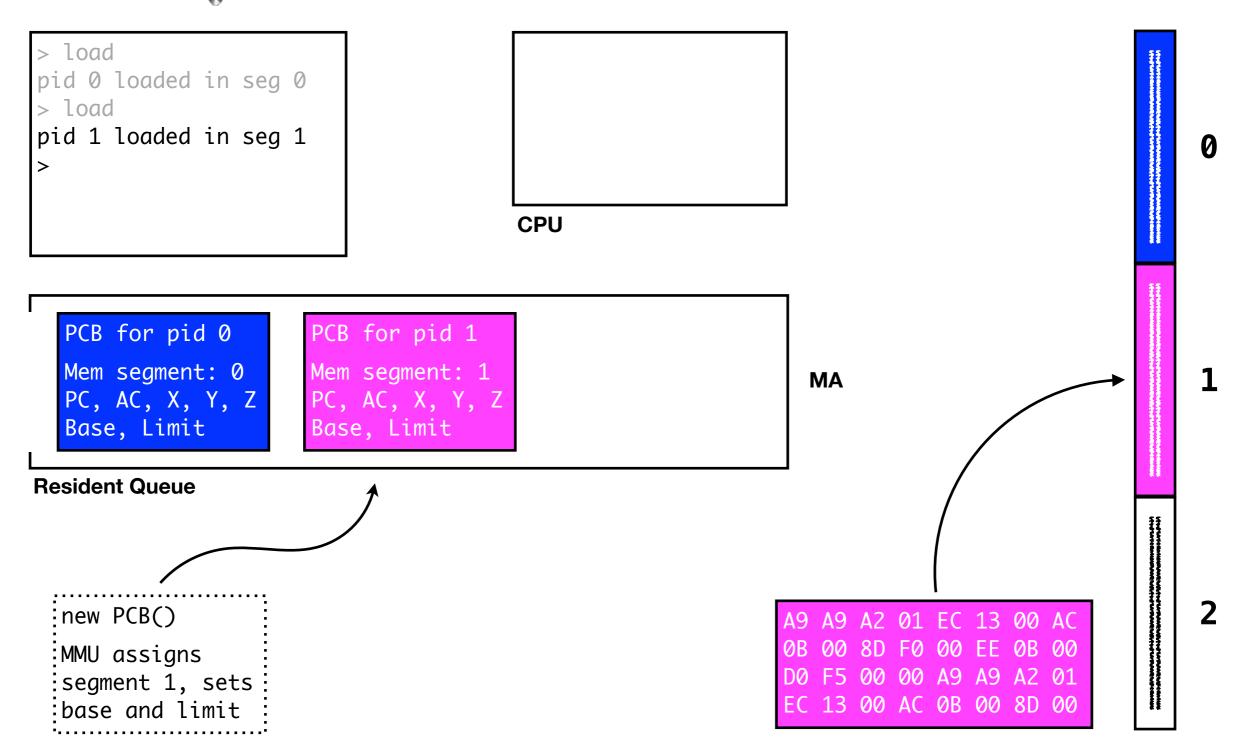

| > load         | CPU |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 |

|----------------|-----|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Resident Queue |     | MA                                                                                                       | ominas phaendan fillendan an filmena ann an ann an ann ann ann an ann an a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 |

|                |     | A9 A9 A2 01 EC 13 00 AC<br>0B 00 8D F0 00 EE 0B 00<br>D0 F5 00 00 A9 A9 A2 01<br>EC 13 00 AC 0B 00 8D 00 | Annual Anthonology of Line Section 2 Line Sections (Line Section 2 Line Section 2 | 2 |

```

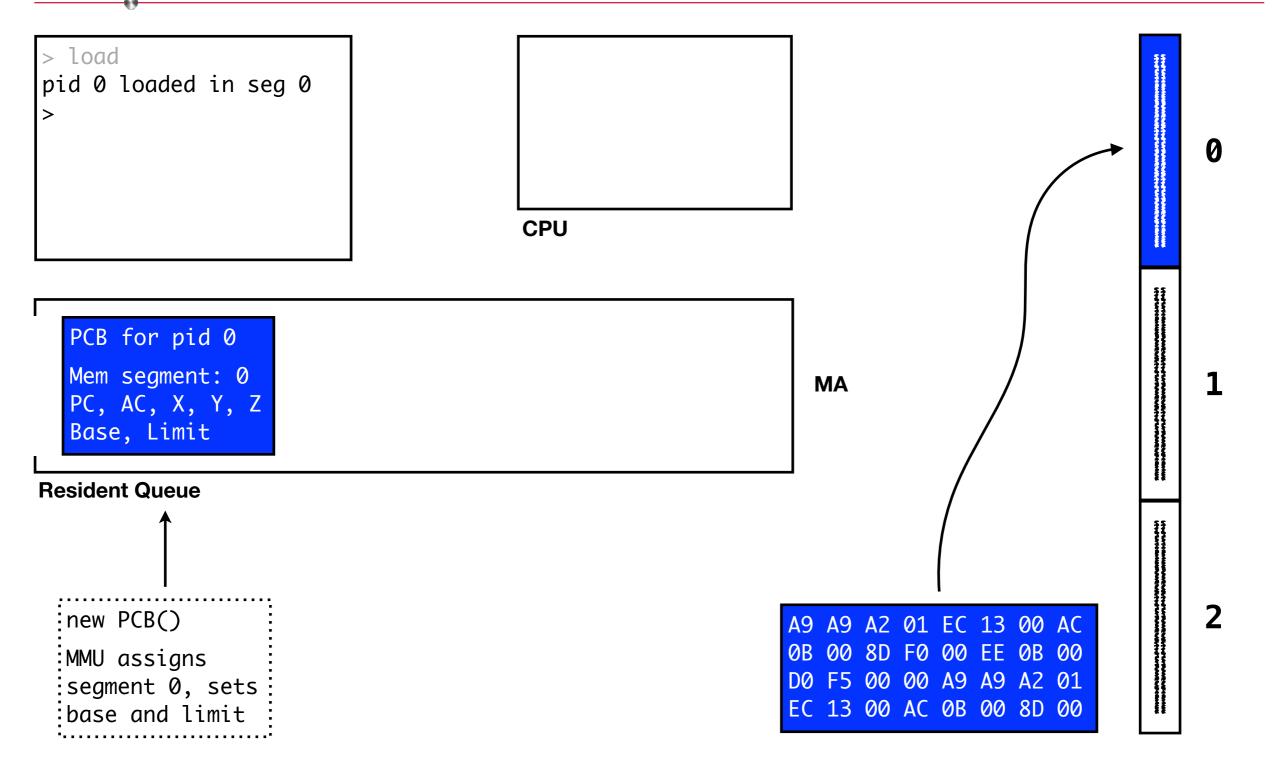

> load

pid 0 loaded in seg 0

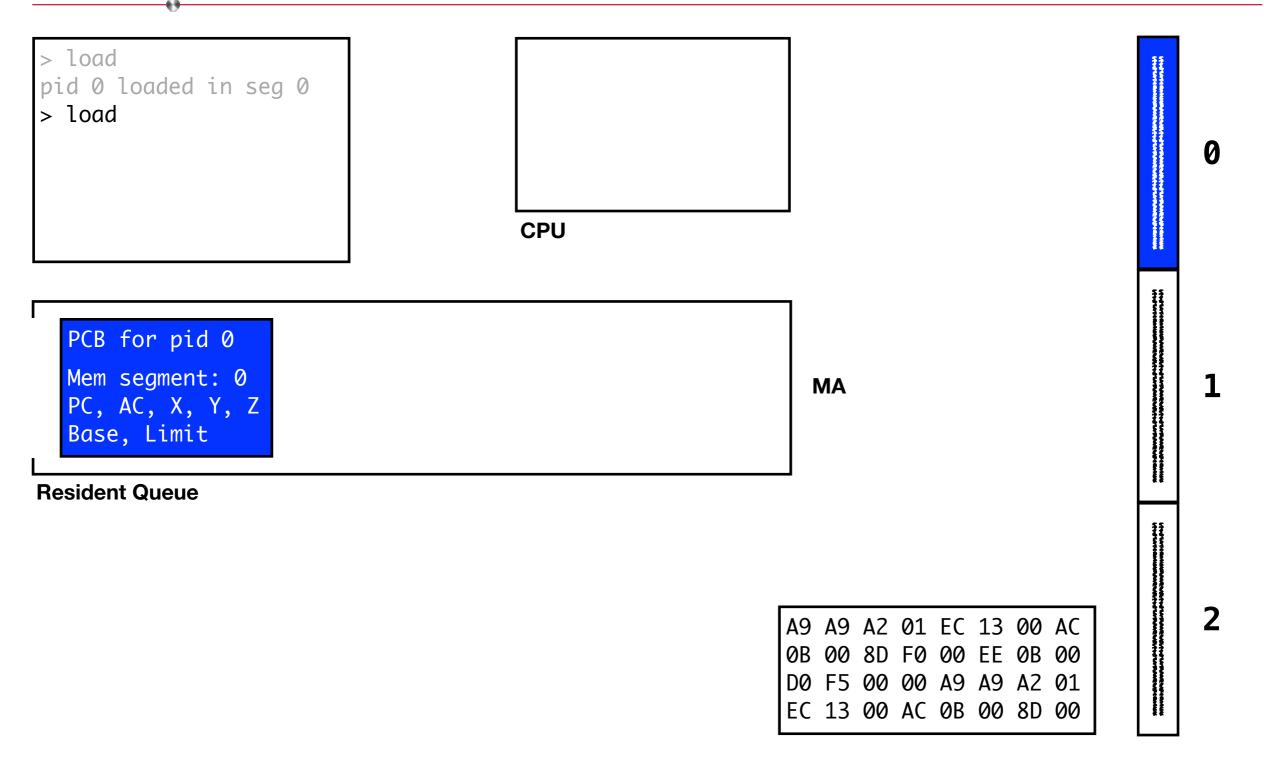

> load

pid 1 loaded in seg 1

> load

CPU

PCB for pid 0

PCB for pid 1

Mem segment: 1

Mem segment: 0

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Resident Queue

A9 A9 A2 01 EC 13 00 AC

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

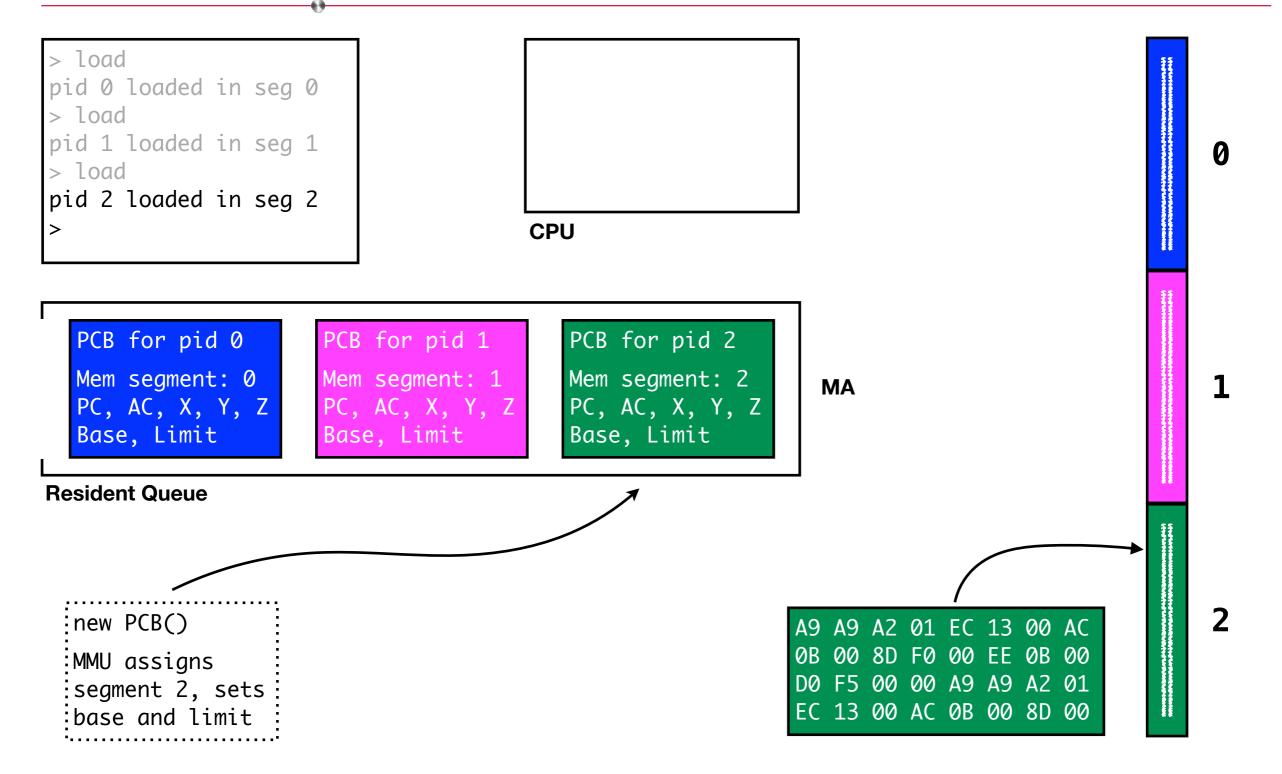

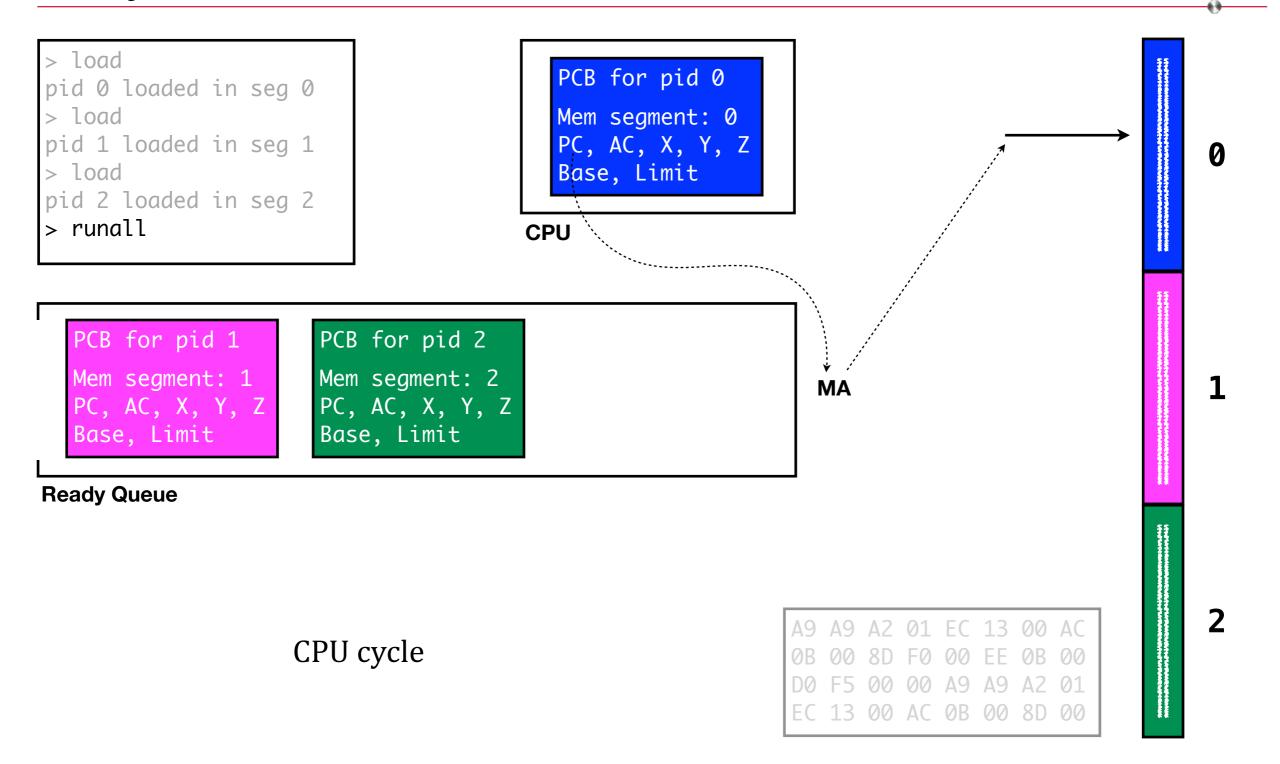

> load

pid 0 loaded in seg 0

> load

pid 1 loaded in seg 1

> load

pid 2 loaded in seg 2

> runall

PCB for pid 0

```

PCB for pid 0

Mem segment: 0

PC, AC, X, Y, Z

Base, Limit

**Resident Queue**

PCB for pid 1

Mem segment: 1

PC, AC, X, Y, Z

Base, Limit

PCB for pid 2

Mem segment: 2

PC, AC, X, Y, Z

Base, Limit

MA

1

2

A9 A9 A2 01 EC 13 00 AC 0B 00 8D F0 00 EE 0B 00 D0 F5 00 00 A9 A9 A2 01 EC 13 00 AC 0B 00 8D 00

```

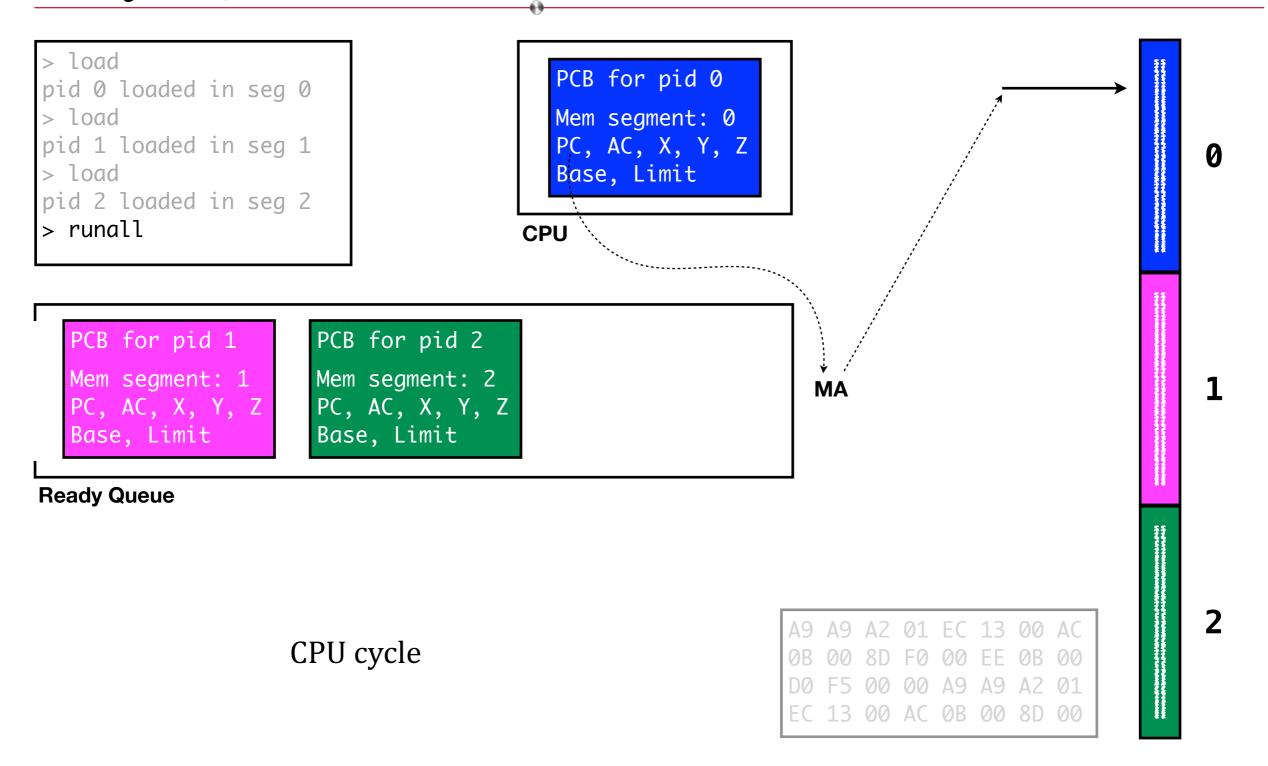

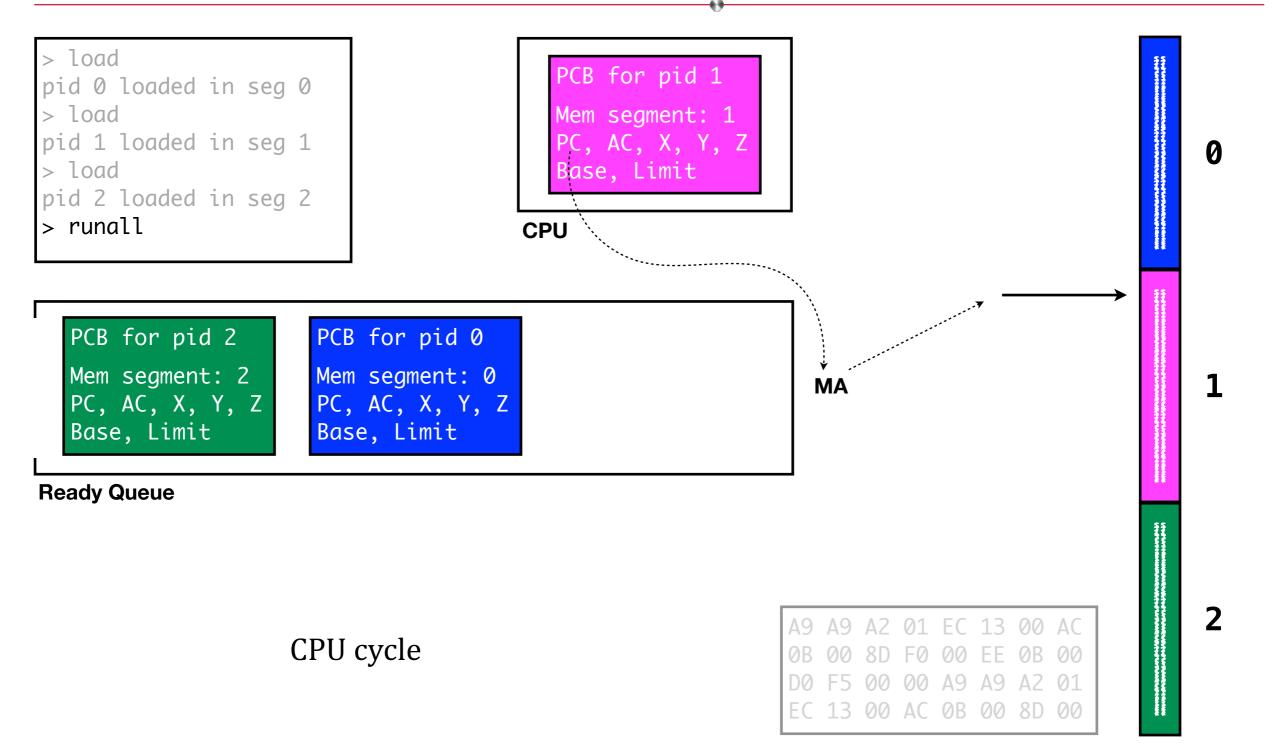

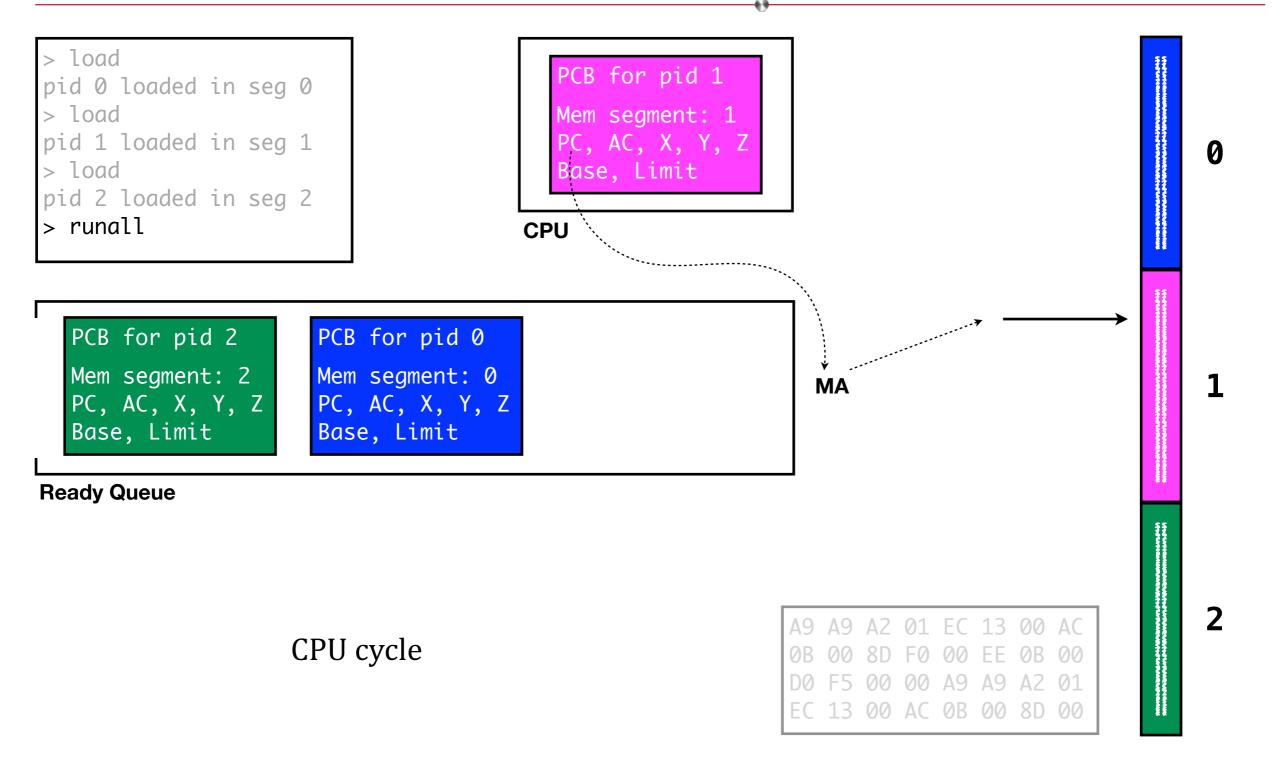

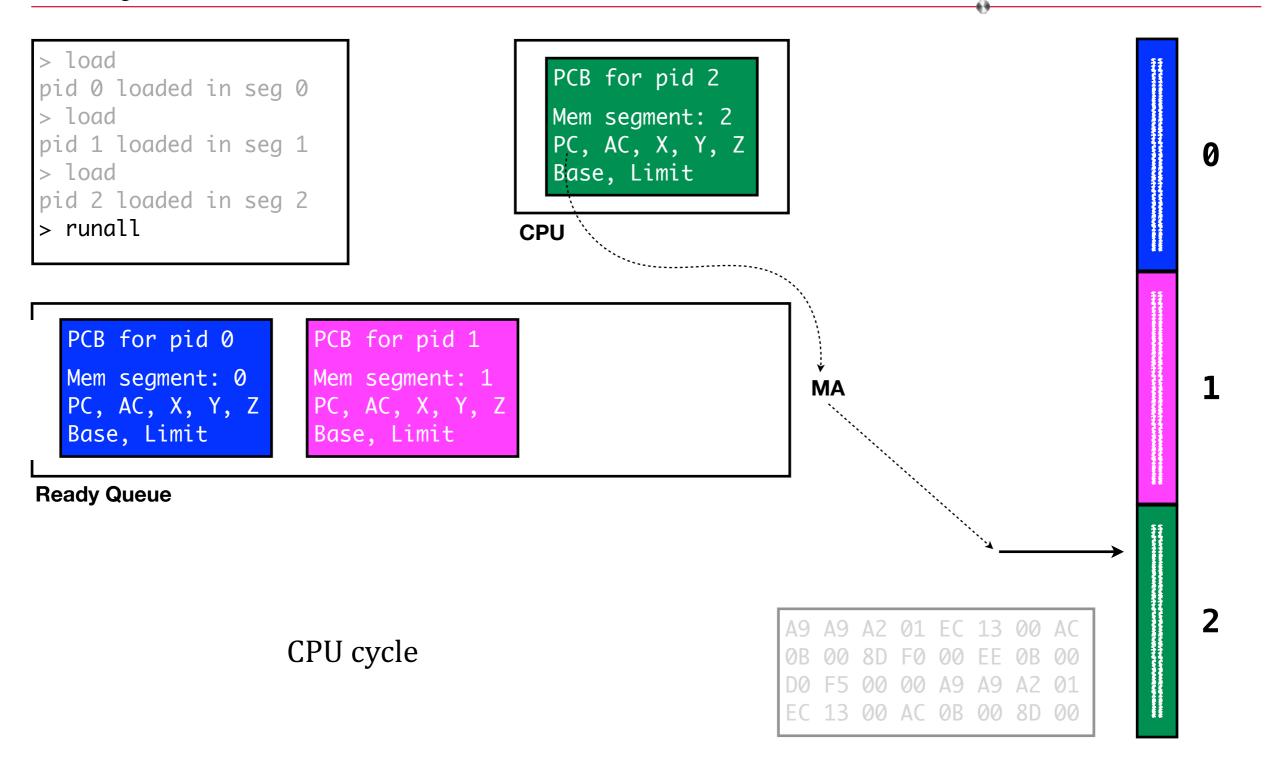

> load

pid 0 loaded in seg 0

> load

pid 1 loaded in seg 1

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 0

PCB for pid 1

Mem segment: 0

Mem segment: 1

Mem segment: 2

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 0

pid 0 loaded in seg 0

> load

Mem segment: 0

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 1

Mem segment: 1

Mem segment: 2

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

```

EC 13 00 AC 0B 00 8D 00

```

> load

PCB for pid 0

pid 0 loaded in seg 0

> load

Mem segment: 0

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 1

Mem segment: 1

Mem segment: 2

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

CPU cycle

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 0

pid 0 loaded in seg 0

Mem segment: 0

> load

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 1

Mem segment: 1

Mem segment: 2

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

pid 0 loaded in seg 0

> load

pid 1 loaded in seg 1

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 1

PCB for pid 0

Mem segment: 1

Mem segment: 2

Mem segment: 0

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 1

pid 0 loaded in seg 0

Mem segment: 1

> load

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 0

Mem segment: 2

Mem segment: 0

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 1

pid 0 loaded in seg 0

Mem segment: 1

> load

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 0

Mem segment: 2

Mem segment: 0

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

pid 0 loaded in seg 0

> load

pid 1 loaded in seg 1

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 2

PCB for pid 0

PCB for pid 1

Mem segment: 2

Mem segment: 0

Mem segment: 1

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 2

pid 0 loaded in seg 0

> load

Mem segment: 2

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 1

PCB for pid 0

Mem segment: 0

Mem segment: 1

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

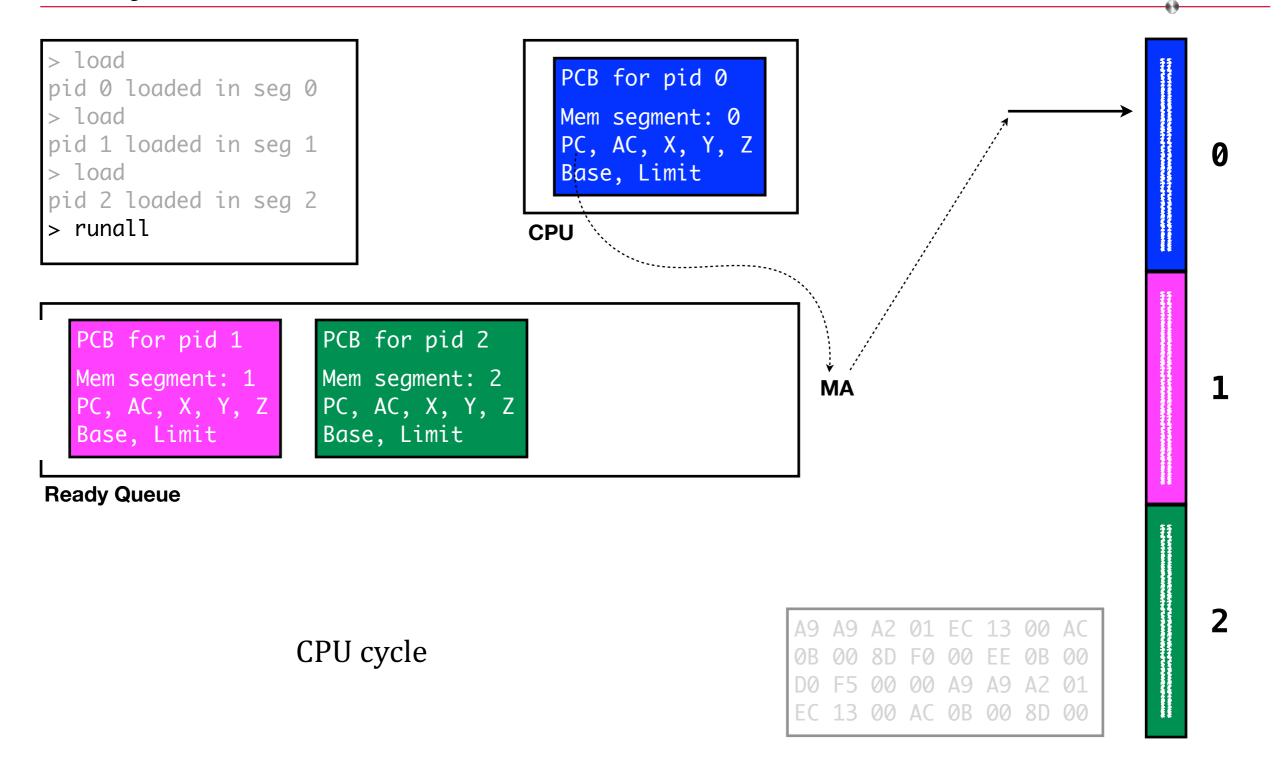

```

> load

PCB for pid 2

pid 0 loaded in seg 0

Mem segment: 2

> load

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 0

PCB for pid 1

Mem segment: 0

Mem segment: 1

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

CPU cycle

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 2

pid 0 loaded in seg 0

> load

Mem segment: 2

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 1

PCB for pid 0

Mem segment: 0

Mem segment: 1

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

```

EC 13 00 AC 0B 00 8D 00

```

> load

pid 0 loaded in seg 0

> load

pid 1 loaded in seg 1

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 1

PCB for pid 0

PCB for pid 2

Mem segment: 0

Mem segment: 1

Mem segment: 2

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

```

```

> load

PCB for pid 0

pid 0 loaded in seg 0

> load

Mem segment: 0

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 1

PCB for pid 2

Mem segment: 2

Mem segment: 1

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

0B 00 8D F0 00 EE 0B 00

D0 F5 00 00 A9 A9 A2 01

```

EC 13 00 AC 0B 00 8D 00

```

> load

PCB for pid 0

pid 0 loaded in seg 0

Mem segment: 0

> load

pid 1 loaded in seg 1

PC, AC, X, Y, Z

Base, Limit

> load

pid 2 loaded in seg 2

> runall

CPU

PCB for pid 1

PCB for pid 2

Mem segment: 2

Mem segment: 1

MA

PC, AC, X, Y, Z

PC, AC, X, Y, Z

Base, Limit

Base, Limit

Ready Queue

A9 A9 A2 01 EC 13 00 AC

Context Switch

F5 00 00 A9 A9 A2 01

EC 13 00 AC 0B 00 8D 00

... and so on, until the processes are complete.

```